最近,铠侠首席技术官 (CTO) Hidefumi Miyajima 表示,计划将在 2031 年批量生产超过 1,000 层的 3D NAND 存储器。不少人感叹,NAND 终究是卷到了 1000 层。

其实,在去年的 IEEE 论坛上,三星也提出了类似的观点,预测到 2030 年将出现 1000 层 NAND。

1000 层 NAND,是「勇者」的游戏。

自推出 3D NAND 闪存以来,NAND 闪存行业在密度和技术方面取得了重大进步。尽管制程困难,但由于其优越的单元特性和比特成本可扩展性,仅用了几年时间,NAND 闪存的主流就从 2D NAND 转向 3D NAND。

回顾 2D NAND,它采用平面架构,浮动栅极 (FG) 和外围电路彼此相邻。2007 年,随着 2D NAND 的尺寸达到极限,东芝提出了 3D NAND 结构。

之后,存储厂商通过在 3D NAND 中使用越来越多的层数来构建更高容量的芯片,从而降低每 GB 的生产成本。

去年 3 月,SK 海力士在会议上发表了 300 层以上 NAND 论文;铠侠推出了第 8 代 BiCS 3D NAND 闪存,为 218 层。5 月,美光推出了 232 层 QLC SSD。8 月,SK 海力士公布了 321 层堆叠 4D NAND Flash 闪存样品。12 月,美光推出了 232 层工作站 SSD。

3D NAND 的层数之战仍在继续。

从理论上讲,堆叠 1000 层以上的 NAND 是可行的,但需要解决堆栈过程中的蚀刻问题,即必须蚀刻具有非常高纵横比的非常深的孔。尽管蚀刻技术在不断进步,但一次性蚀刻更深的孔具有很大的挑战,也无法提高蚀刻速度。而以沉积和蚀刻为主的工艺流程也堆栈如此多层数的话,将无法降低成本。

除了蚀刻之外,还需要用非常薄的介电层上下均匀地填充这个孔,而沉积几纳米的层并不容易,仍然具有挑战性。

对于如何加高 NAND 层数,不同存储企业有不同的方式。

在 3D NAND 中,最终的目标是在基板上堆叠更多层,从而实现更高的密度。目前主要有两种堆叠方式——单层或者双层。

传统上,采用的是单层方法。例如,三星的 92 层 3D NAND 器件将所有 92 层堆叠在同一芯片上,其 128 层也同样是在同一芯片上堆叠了 128 层。

这种将所有层数堆叠在一个芯片上的方式,可以让存储厂商降低成本和开发时间。但是到 128 层的时候,就是单层的极限。这里的一个大问题就是刻蚀,目前一次性刻蚀达到 128 层就比较困难了。

然后,存储厂商将主意打在了双层上。就是比如一个 96 层的 NAND,是将两个 48 层结构堆叠在一起。美光的 176 层器件,就是采用这种方式,将两个 88 层结构堆叠在一起。双层的好处就在于,更少的层数更容易进行刻蚀。

不过,在达到 300 层时,双层似乎也不管用了,业内认为在制造 300 层芯片时,最常用的应该还是三层堆叠。也有机构表示,三星明年下半年推出的第十代 430 层 NAND,将会采用三层堆叠的方式。

三星:V-NAND 架构

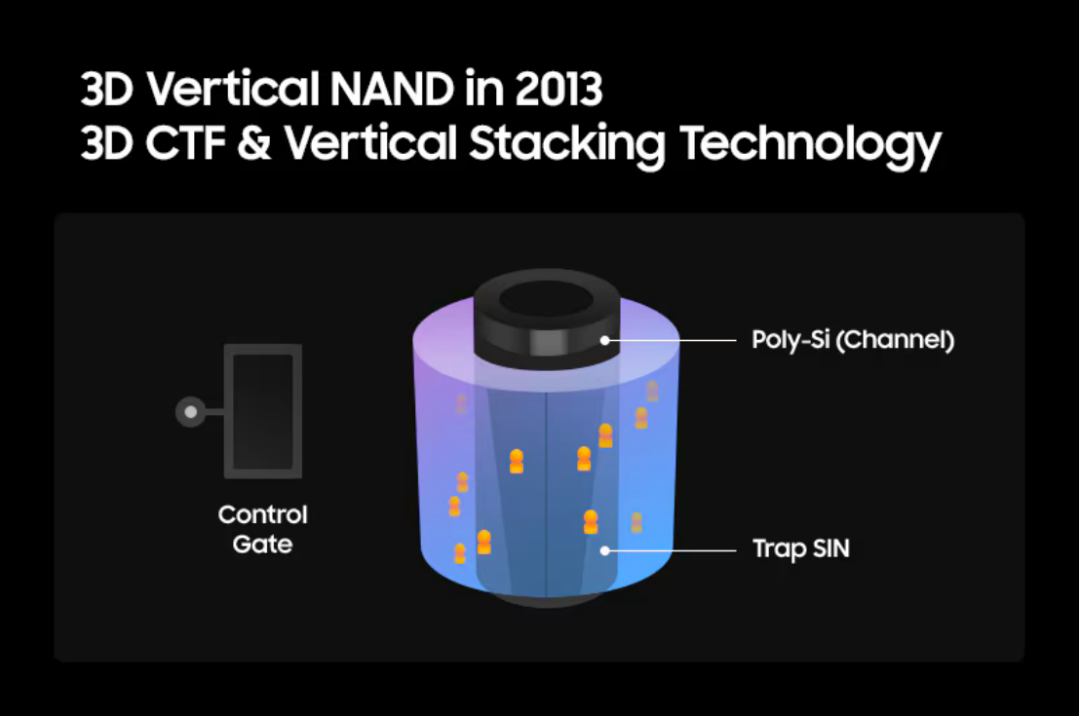

三星于 2013 年率先向市场推出「V-NAND」(V 代表 Vertical,垂直的意思)。

V-NAND 技术采用不同于传统 NAND 闪存的排列方式,通过改进型的 Charge Trap Flash 技术,在一个 3D 的空间内垂直互连各个层面的存储单元,使得在同样的平面内获得更多的存储空间。

一张显示浮栅、电荷撷取闪存 (CTF) 以及 3D 垂直 NAND (V-NAND) 技术进展的展示图

此外,三星 V-NAND 闪存还放弃浮栅极 MOSFET,使用电荷攫取闪存(charge trap flash,简称 CTF)设计。每个 cell 单元看起来更小了,但里面的电荷是储存在一个绝缘层而非之前的导体上,理论是没有消耗的。这种更小的电荷有很多优点,比如更高的可靠性、更小的体积。

虽然三星推出的第一款 3D NAND 堆叠层数仅为 24 层,但在当时却打破了平面技术的瓶颈,并使 3D NAND Flash 从技术概念推向了商业市场。

之后的 10 年间,三星推出了数代产品,以维护自己在 NAND 闪存市场的地位。如 2020 年推出的 176 层的第七代「V-NAND」。

到目前,三星正在开发的是 300 层的第九代 V-NAND,还是使用的双层堆叠技术,预计今年就将投入生产。

铠侠:BiCS 架构

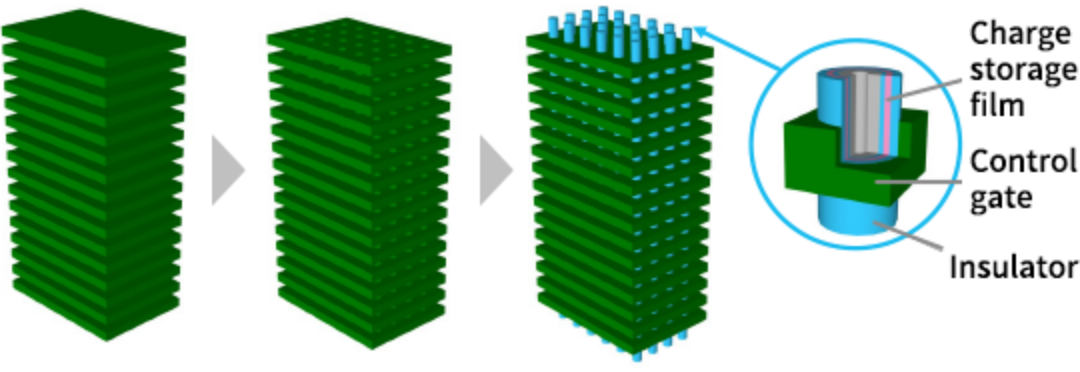

冲头和塞子的基本流程

BiCS 架构是铠侠在 2007 年提出的概念。在 BiCS FLASH 中,充当控制栅极的板状电极(上图中的绿色板)和绝缘体交替堆叠,然后立即垂直开出(打孔)大量孔到表面。接下来,用电荷存储膜(粉红色所示的部分)和柱状电极(灰色所示的柱结构)填充(塞住)板状电极中开设的孔的内部。在此条件下,板状电极与柱状电极的交点即为一个存储单元。

BiCS FLASH 存储单元

可以看一下 BiCS FLASH 存储单元的放大视图。在 BiCS FLASH 存储单元中,电子在穿过柱中心的电极(灰色所示的结构)和电荷存储薄膜(粉色)之间交换。

这样,不是一次一层地堆叠存储单元,而是首先堆叠板状电极,然后在板状电极上开孔并连接电极,从而为所有层形成存储单元一次性完成所有操作,以降低制造成本。

自 2007 年在学术会议上提出 BiCS FLASH「批量处理技术」概念以来,BiCS FLASH 产品已于 2015 年实现 48 层、2018 年 96 层、2020 年 112 层、2020 年 162 层的商用化。

目前,铠侠最好的 3D NAND 器件是第八代 BiCS 3D NAND 存储器。新闪存包含四个平面(plane),应用了先进的晶圆键合、横向收缩技术,并在横向收缩、纵向收缩方面取得平衡,存储密度比上代提升超过 50%,达到了 1Tb(128GB)。

值得一提的是,西数、铠侠开发了新的 CBA 技术,也就是将 CMOS 直接键合在阵列之上(CMOS directly Bonded to Array),每个 CMOS 晶圆、单元阵列晶圆都使用最适合的技术工艺独立制造,再键合到一起,从而大大提升存储密度、I/O 速度。

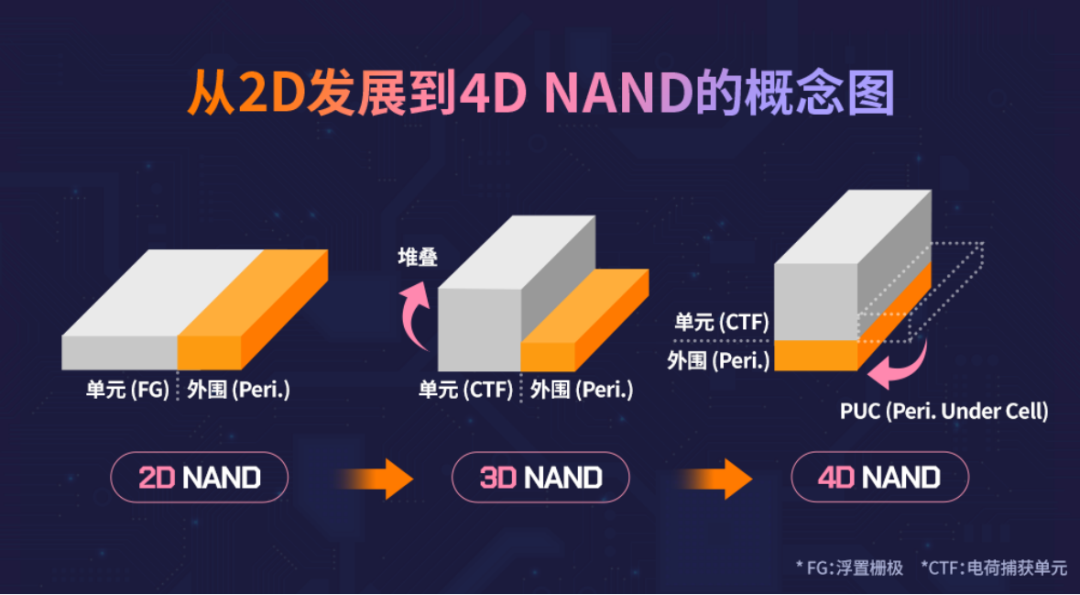

SK 海力士:4D NAND

SK 海力士将自己的堆叠方式称为 4D NAND。在 2018 年,SK 海力士就推出了 96 层的 4D NAND。

2D NAND 到 4D NAND 的发展概念图 来源:SK 海力士

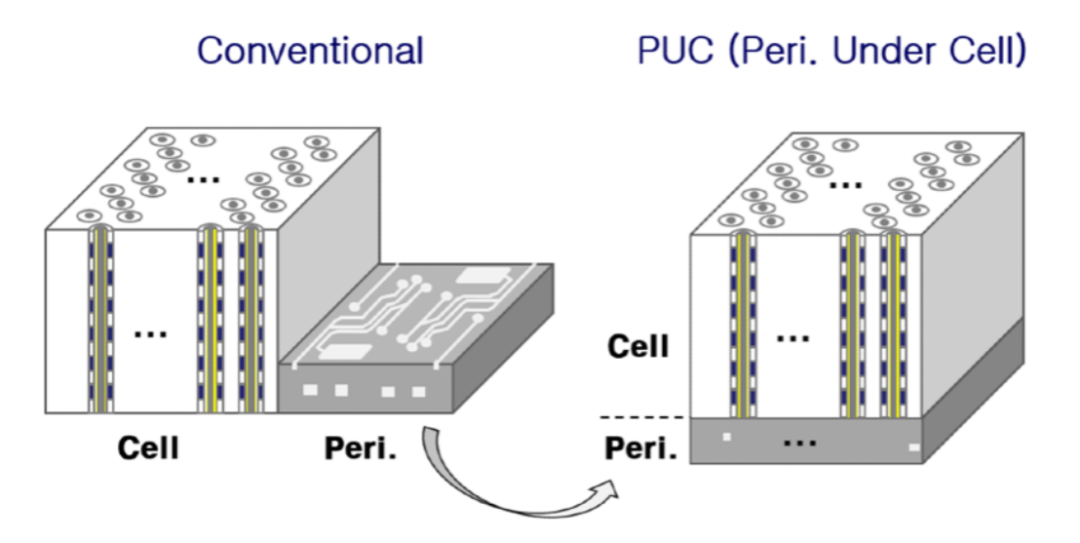

传统的 3D NAND 架构由堆叠的 NAND 阵列和外围电路组成。外围电路控制阵列并管理存储器读取和写入。在大多数设计中,外围电路放置在 3D NAND 阵列旁边。这种布局占用了裸片区域,并最终限制了可用于内存本身的区域数量。

SK 海力士将过去放置在存储单元旁侧的外围电路转移至存储单元下方,减少了芯片占用空间。并将其称之为 4D NAND。据 SK 海力士的说法,其之后推出的 128 层 1Tb TLC 4D NAND,生产效率和成本效益分别提高了 40% 和 60%。

外围电路是 4D NAND 的底层

更具体的,我们还可以看 SK 海力士最新的 321 层 NAND。每个硅芯片可提供 1Tbit 的存储容量,同时利用 3 位/单元 (TLC) 多级存储方法,与前代产品相比,该增强版本的存储密度提高了 41%,读取延迟降低了 13%,写入吞吐量提高了 12%,读取功耗降低了 10%。

在堆叠方式上,也于惯例有所不同,并不是采用双层堆叠 150 层,而是选择了三层堆叠,每个堆栈包含 107 层。

在 300 层以上 NAND 方面,SK 海力士的 NAND 开发主管 Jungdal Choi 在一场演讲中放言:「凭借解决堆叠限制的另一项突破,SK 海力士将开启 300 层以上 NAND 时代并引领市场。」

其实 4D NAND 背后的概念,在其他地方使用过。比如,英特尔和美光等公司之前在其 3D NAND 中采用了相同的架构,但将其称为「CMOS under Array」(CuA)技术。

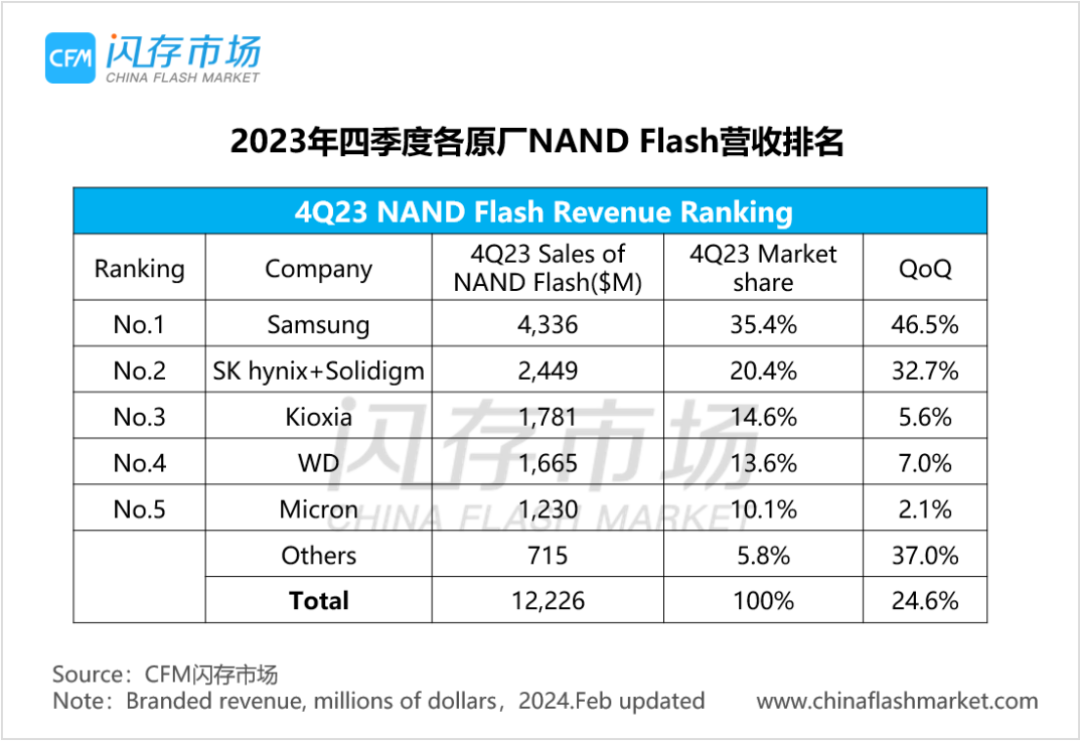

NAND 市场依旧焦灼。从市场份额来看,2023 年第四季度,三星仍牢牢占据着 NAND 闪存市场的头把交椅。

三星四季度 NAND Flash 销售收入 43.36 亿美元,环比增长 46.5%,市场份额 35.4%;SK 海力士(包括 Solidigm)四季度 NAND Flash 销售收入为 24.49 亿美元,环比增长 32.7%,市场份额为 20.4%;铠侠四季度 NAND Flash 销售收入为 17.81 亿美元,环比增长 5.6%,市场份额为 14.6%;西部数据四季度 NAND Flash 销售收入为 16.65 亿美元,环比增长 7.0%,市场份额为 13.6%。

此外,NAND 闪存产业链动态频出,部分厂商表示有提价或提高产能利用率的意愿。NAND 的市场价格也在快速上涨。

今年 2 月,NAND 闪存通用产品的 2 月份平均固定交易价格为 4.9 美元。尽管第二季 NAND Flash 采购量较第一季小幅下滑,但整体市场氛围持续受供应商库存降低,以及减产效应影响,预估第二季 NAND Flash 合约价将强势上涨约 13%~18%。

从市场动态和需求变化来看,NAND Flash 正在经历新一轮的变革。

结语

NAND 闪存结构从最初的 2D 到如今的 3D、4D,层数不断提高,24 层、36 层、48 层、96 层、128 层、176 层、200+层,到最近三星规划的 1000 层,半导体从业者对技术的追求没有止境。

曾经在 2016 年,专家指出,由于技术问题,3D NAND 可能会在 300 层或接近 300 层时失去动力。但到了今天,这似乎并不是问题。

Objective Analysis 首席分析师吉姆·汉迪 (Jim Handy) 表示:「实际上是没有物理限制的。在半导体领域,总是有人说我们做不到。之前,有人说我们无法进行 20 纳米以下的光刻。现在,他们正在研究 1 纳米。三星谈到了 1000 层。20 年后,我们可能会嘲笑我们曾经认为这已经很多了。」

*声明:本文系原作者创作。文章内容系其个人观点,我方转载仅为分享与讨论,不代表我方赞成或认同,如有异议,请联系15950995158。